EDB: parameterized design#

This example shows how to

Set up an HFSS project using SimulationConfiguration class.

Create automatically parametrized design.

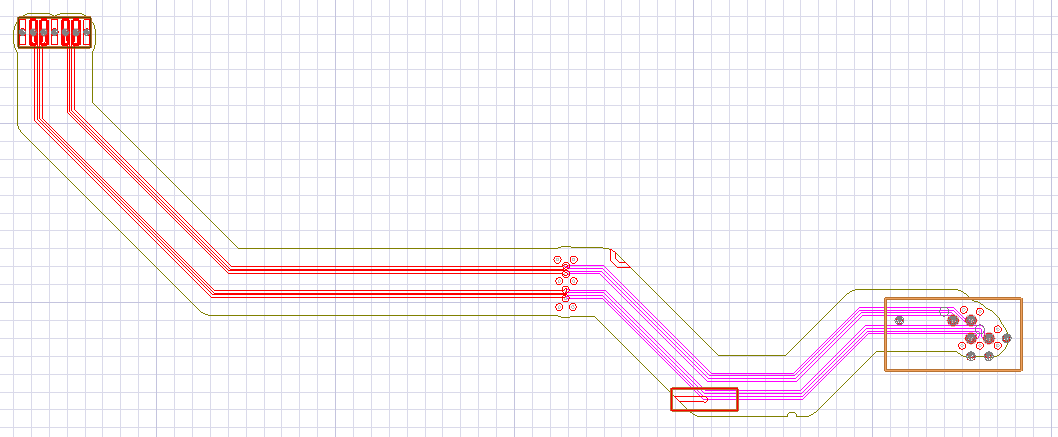

This image shows the layout created in this example:

Import dependencies.#

[1]:

import tempfile

[2]:

import ansys.aedt.core

[3]:

import pyedb

from pyedb.misc.downloads import download_file

Create an instance of a pyedb.Edb object.#

[4]:

temp_dir = tempfile.TemporaryDirectory(suffix=".ansys")

target_aedb = download_file("edb/ANSYS-HSD_V1.aedb", destination=temp_dir.name)

print("Project is located in ", target_aedb)

# Select EDB version (change it manually if needed, e.g. "2024.2")

edb_version = "2024.2"

print(f"EDB version: {edb_version}")

edb = pyedb.Edb(edbpath=target_aedb, edbversion=edb_version)

print("AEDB file is located in {}".format(target_aedb))

Project is located in C:\Users\ansys\AppData\Local\Temp\tmpkxk9ljtj.ansys\edb/ANSYS-HSD_V1.aedb

EDB version: 2024.2

PyAEDT INFO: Logger is initialized in EDB.

PyAEDT INFO: legacy v0.37.0

PyAEDT INFO: Python version 3.10.11 (tags/v3.10.11:7d4cc5a, Apr 5 2023, 00:38:17) [MSC v.1929 64 bit (AMD64)]

PyAEDT INFO: Database ANSYS-HSD_V1.aedb Opened in 2024.2

PyAEDT INFO: Cell main Opened

PyAEDT INFO: Builder was initialized.

PyAEDT INFO: EDB initialized.

AEDB file is located in C:\Users\ansys\AppData\Local\Temp\tmpkxk9ljtj.ansys\edb/ANSYS-HSD_V1.aedb

Prepare the layout for the simulation#

The new_simulation_configuration() method creates an instance of the SimulationConfiguration class. This class helps define all preprocessing steps required to set up the PCB for simulation. After the simulation configuration has been defined, they are applied to the EDB using the Edb.build_simulation() method.

[5]:

simulation_configuration = edb.new_simulation_configuration()

simulation_configuration.signal_nets = [

"PCIe_Gen4_RX0_P",

"PCIe_Gen4_RX0_N",

"PCIe_Gen4_RX1_P",

"PCIe_Gen4_RX1_N",

]

simulation_configuration.power_nets = ["GND"]

simulation_configuration.components = ["X1", "U1"]

simulation_configuration.do_cutout_subdesign = True

simulation_configuration.start_freq = "OGHz"

simulation_configuration.stop_freq = "20GHz"

simulation_configuration.step_freq = "10MHz"

Now apply the simulation setup to the EDB.

[6]:

edb.build_simulation_project(simulation_configuration)

PyAEDT INFO: Building simulation project.

PyAEDT INFO: Cutting out using method: 1

PyAEDT INFO: Cutting out using method: 1

PyAEDT INFO: Cutout Multithread started.

PyAEDT INFO: Net clean up Elapsed time: 0m 2sec

PyAEDT INFO: Correctly computed Extension at first iteration.

PyAEDT INFO: Extent Creation Elapsed time: 0m 0sec

PyAEDT INFO: 2022 Padstack Instances deleted. Elapsed time: 0m 1sec

PyAEDT INFO: 446 Primitives deleted. Elapsed time: 0m 2sec

PyAEDT INFO: 1010 components deleted

PyAEDT INFO: Deleted 472 components

PyAEDT INFO: Single Pins components deleted Elapsed time: 0m 0sec

PyAEDT INFO: Cutout completed. Elapsed time: 0m 5sec

PyAEDT INFO: Cutout processed.

PyAEDT INFO: Deleting existing ports.

PyAEDT INFO: Creating HFSS ports for signal nets.

PyAEDT INFO: Number of ports: 8

PyAEDT INFO: Configure HFSS extents.

PyAEDT INFO: Adding frequency sweep

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: Padstack definition with zero plating ratio, defaulting to 20%

PyAEDT INFO: EDB file save time: 0.00ms

[6]:

True

Parameterize#

The layout can automatically be set up to enable parametric studies. For example, the impact of antipad diameter or trace width on signal integrity performance may be invested parametrically.

[7]:

edb.auto_parametrize_design(layers=True, materials=True, via_holes=True, pads=True, antipads=True, traces=True)

edb.save_edb()

edb.close_edb()

PyAEDT INFO: EDB file save time: 15.63ms

PyAEDT INFO: EDB file release time: 0.00ms

[7]:

True

Open project in AEDT#

All manipulations thus far have been executed using the EDB API, which provides fast, streamlined processing of layout data in non-graphical mode. The layout and simulation setup can be visualized by opening it using the 3D Layout editor in AEDT.

Note that there may be some delay while AEDT is being launched.

[8]:

hfss = ansys.aedt.core.Hfss3dLayout(

projectname=target_aedb,

specified_version=edb_version,

non_graphical=False,

new_desktop_session=True,

)

PyAEDT WARNING: Argument `projectname` is deprecated for method `__init__`; use `project` instead.

PyAEDT WARNING: Argument `specified_version` is deprecated for method `__init__`; use `version` instead.

PyAEDT WARNING: Argument `new_desktop_session` is deprecated for method `__init__`; use `new_desktop` instead.

PyAEDT INFO: Python version 3.10.11 (tags/v3.10.11:7d4cc5a, Apr 5 2023, 00:38:17) [MSC v.1929 64 bit (AMD64)]

PyAEDT INFO: PyAEDT version 0.14.dev0.

PyAEDT INFO: Initializing new Desktop session.

PyAEDT INFO: Log on console is enabled.

PyAEDT INFO: Log on file C:\Users\ansys\AppData\Local\Temp\pyaedt_ansys_90be46f1-14a4-487a-9c55-c41b191e1a6b.log is enabled.

PyAEDT INFO: Log on AEDT is enabled.

PyAEDT INFO: Debug logger is disabled. PyAEDT methods will not be logged.

PyAEDT INFO: Launching PyAEDT with gRPC plugin.

PyAEDT INFO: New AEDT session is starting on gRPC port 55755

PyAEDT INFO: AEDT installation Path C:\Program Files\AnsysEM\v242\Win64

PyAEDT INFO: Ansoft.ElectronicsDesktop.2024.2 version started with process ID 12584.

PyAEDT INFO: EDB folder C:\Users\ansys\AppData\Local\Temp\tmpkxk9ljtj.ansys\edb/ANSYS-HSD_V1.aedb has been imported to project ANSYS-HSD_V1

PyAEDT INFO: Active Design set to 0;main

PyAEDT INFO: Aedt Objects correctly read

The following cell can be used to ensure that the design is valid for simulation.

[9]:

validation_info = hfss.validate_full_design()

is_ready_to_simulate = True

PyAEDT INFO: #### Design Validation Checks###

PyAEDT INFO: **** Validation Completed Correctly

PyAEDT INFO: Ports Requested: None

PyAEDT INFO: Ports Defined: 8

PyAEDT INFO: Excitation name: U1.AN26.PCIe_Gen4_RX0_N

PyAEDT INFO: Excitation name: U1.AP25.PCIe_Gen4_RX1_N

PyAEDT INFO: Excitation name: U1.AP26.PCIe_Gen4_RX0_P

PyAEDT INFO: Excitation name: U1.AR25.PCIe_Gen4_RX1_P

PyAEDT INFO: Excitation name: X1.A2.PCIe_Gen4_RX0_P

PyAEDT INFO: Excitation name: X1.A3.PCIe_Gen4_RX0_N

PyAEDT INFO: Excitation name: X1.A5.PCIe_Gen4_RX1_P

PyAEDT INFO: Excitation name: X1.A6.PCIe_Gen4_RX1_N

[10]:

for s in validation_info[0]:

if "error" in s:

print(s)

is_ready_to_simulate = False

if is_ready_to_simulate:

print("The model is ready for simulation.")

else:

print("There are errors in the model that must be fixed.")

The model is ready for simulation.

Release the application from the Python kernel#

It is important to release the application from the Python kernel after execution of the script. The default behavior of the release_desktop() method closes all open projects and closes the application.

If you want to continue working on the project in graphical mode after script execution, call the following method with both arguments set to False.

[11]:

hfss.release_desktop(close_projects=True, close_desktop=True)

temp_dir.cleanup() # Remove the temporary folder and files. All data will be removd!

PyAEDT INFO: Desktop has been released and closed.